|

RADIO INSTITUTO CURSO DE CIRCUITOS DIGITALES LECCIÓN

Nº 2 TRANSISTORES EN CIRCUITOS DE CONMUTACIÓN A.O. COMO SCHMITT-TRIGGER - TENSIÓN OFFSET -

CONMUTACIÓN DE RELÉS - ESTADOS NO ABSOLUTOS - UBICACIÓN DE LA CARGA - CORTE

PROFUNDO - DISIPACIÓN DE POTENCIA - CONMUTACIÓN DE CARGAS EN 12 V DESDE

CIRCUITOS DE 5 V - ACOPLAMIENTOS CMOS A TTL Y TTL A CMOS - CARACTERÍSTICAS DE

INTEGRADOS CMOS - CARACTERÍSTICAS DE INTEGRADOS TTL - TABLA DE VERDAD NAND Continuamos en esta lección con el

estudio del comportamiento de los transistores en circuitos digitales y las

variantes que se pueden lograr con ellos. CONMUTACIÓN CON ESTADOS NO

ABSOLUTOS: Muchas veces nos encontramos con

circuitos digitales que emplean en alguna parte de los mismos, amplificadores

operacionales (AO) conectados como SCHMITT-TRIGGER o comparadores, es decir

que cambian de estado su salida según el potencial que tienen en sus dos

entradas. Cuando la entrada no inversora (+) es mas positiva que la inversora

(-) la salida es de nivel alto (1). Por el contrario si la entrada

inversora fuese mas positiva que la no

inversora, la salida corresponde a un nivel bajo (0). Considerando siempre

una alimentación de 12 V, se observa que éstos dos niveles no son absolutos

como ocurre con los integrados digitales ya que el 1 no corresponde a 12 V

sino un poco menos, alrededor de 11 V, y el 0 suele tener todavía una diferencia

mayor, debido a un remanente denominado tensión de offset y

sabe quedar en 1,5 V aproximadamente (no en todos los casos). Si ésta salida se aplica a la

entrada de un integrado digital, también alimentado con 12 V, no hay

problemas, dado que el mismo interpreta entre 0 V y casi 6 V un nivel bajo

(0), y entre un poco mas de 6 V y 12 V un nivel alto (1). Decimos casi 6 V porque en éste

estado, denominado intermedio, existe una indecisión en la operatividad del

mismo. Pero si tenemos la necesidad de conmutar un transistor con ésta

salida, se presenta el inconveniente que no se puede llevar al corte ningún

transistor, sea NPN o PNP. Tratándose de un NPN, el motivo es

que la base siempre queda positiva ya que el "0" que entrega el

operacional, es en realidad de 1,5 V, superior a los 0,7 V necesarios para su

conducción, de todos modos aunque ésta salida fuera de 0,5 V, con lo cual el

transistor pasará al estado de corte, no conviene dejarlo en ésta situación

porque estará trabajando en un límite crítico y cualquier espúrio de línea que pueda aparecer superando un

poco éste valor, lo hará conducir. Siempre hay que tratar de llevarlo al

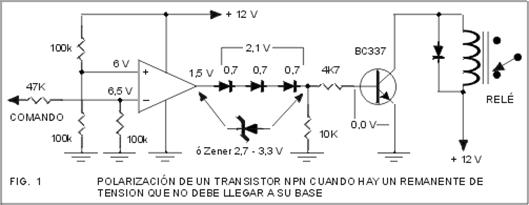

corte neto y mantenerlo con 0 V entre base y emisor. En la figura 1 vemos como se logra

superar este inconveniente. A modo de ejemplo ilustramos un caso donde el

transistor debe conmutar un relé de baja intensidad

de corriente en su bobina, y alimentamos todo el circuito con una fuente de

12 V. Se observa que la entrada inversora

(-) es un poco mas positiva que la no inversora (+), concretamente 6,5 V

contra 6 V, en éstas condiciones el estado de salida es de nivel bajo (0)

pero con el remanente offset de 1,5 V ya

explicado.

Vemos que la entrada + del

operacional está a un nivel medio de la tensión de fuente, dada por el

divisor de tensión que forman las dos resistencias de 100 K. La entrada -

(menos) es la que utilizamos para el comando y tiene también a masa una

resistencia de 100 K y una de 47 K, que puede ser de valor distinto a

condición que sea de menor valor que la de masa. Esta resistencia es

hipotéticamente la que viene de un circuito anterior de comando. Cuando la

tensión de comando desciende ó directamente pasa a cero, la entrada - queda

por debajo de la entrada + y el operacional cambia al estado alto. En estado alto (1) la base del

transistor se polariza con tensión positiva de valor amplio y se satura sin inconvenientes.

En estado bajo, la tensión offset de 1,5

V, queda neutralizada por los tres diodos de silicio que hemos puesto en

serie con la alimentación de base. En efecto, cada diodo tiene una

caída de 0,7 V, de modo que la suma de los tres nos da una caída total de 2,1

V., por lo tanto el remanente de 1,5 V por ser menor no llega a la base.

Los tres diodos pueden

reemplazarse por un zener de 2,7 V

ó mas y se obtiene el mismo resultado.

Ahora veamos esta misma situación, pero utilizando un transistor PNP. Fig. 2 Como vemos, este circuito es muy

similar al anterior, solo que está adecuado al uso de un transistor PNP.

Ahora es la entrada + la que usamos para el comando, aunque bien podría haber

sido la -, lo que importa es la diferencia de magnitud entre una y la otra. Tenemos la entrada + con mayor

tensión que la - y como ésta no invierte, en la salida tenemos el estado alto

(1) que como ya dijimos es de 11 V. Esta tensión no es suficiente para

mantener al corte el transistor, por ello polarizamos su base con la

resistencia de 10 K conectada a + 12 V, y conectamos en serie con la

resistencia de 4,7 K dos diodos de silicio para obtener una caída de 1,4 V. De éste modo tenemos la salida del

operacional en 11 V, que viene a ser un punto negativo de 1 V con respecto a

la tensión de fuente y por ende a la tensión de base. Como los diodos

introducen una caída de 1,2 a 1,4 V, que supera ésta diferencia de

1 V, no circulará corriente por ellos, y la base se mantendrá en 12 V, con lo

cual el transistor se mantiene al corte. Cuando el operacional cambia al

estado bajo, circula por ésta red la corriente de base y el transistor entra

en conducción. En ese instante la tensión que se puede medir entre base y

emisor es de 0,7 V, positivo en el emisor, y si la medición se hace con

respecto a masa, se leerá 11,3 V aproximadamente, siempre que la tensión de

+B de fuente se mantenga en 12 V. COMO LOGRAR UN CORTE PROFUNDO. Existen también ciertas ocasiones

donde posibles ruidos de línea o alguna otra interferencia, que se

manifiestan en pulsos de distinta amplitud que podrían llegar a la base de

los transistores de los ejemplos citados, u otros en montaje distinto, que

pueden provocar disparos erráticos en los mismos. En éstas condiciones conviene

mantenerlos a un corte mas profundo e incluso filtrar la entrada en base, de

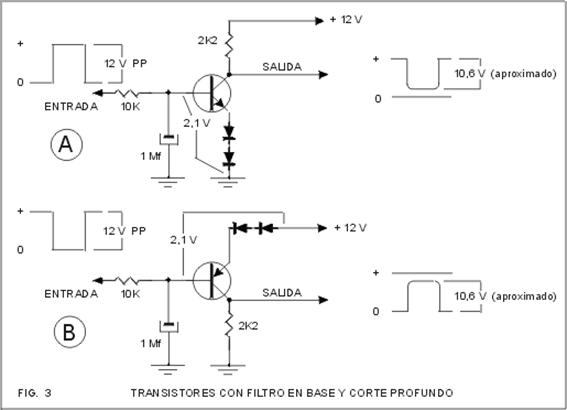

manera de evitar éstos falsos disparos. La solución a éstos problemas

es sencilla como podemos ver en la Figura 3.

En ésta figura podemos apreciar que las bases de ambos

transistores tienen conectado un electrolítico a masa, que se encarga de absorber

los posibles pulsos de interferencia, los valores que se expresan en los

componentes son a título de ejemplo, pues pueden ser otros. Debemos tener en cuenta que al

introducir un capacitor en la base se

produce una constante de tiempo de carga y descarga del mismo, que modifica

la señal de salida, redondeando un poco los flancos ascendente y descendente. Esto puede acarrear problemas de

incompatibilidad con la entrada de algunos integrados que no toman esta

señal, solo lo hacen con señales perfectamente cuadradas. Si sucede esto, se soluciona

intercalando un separador disparador SCHMITT, mas adelante estudiaremos éstos

integrados. Además hemos puesto en serie con los emisores dos diodos para

elevar el umbral de conducción de los transistores. En efecto, teniendo en cuenta la

caída de 0,7 V de éstos componentes, es fácil deducir que éstos valores se

suman a los 0,7 V propios del transistor, con lo que conseguimos que en ésta

disposición conducirá cuando en base tengamos una diferencia de 2,1 V con respecto

a masa en el transistor NPN, y a +B en el PNP. De ésta manera hemos triplicado el

umbral de conducción, o lo que es lo mismo profundizamos tres veces el corte.

Si fuera necesario se puede agregar o disminuir la cantidad de diodos, con lo

que se modifica dicho umbral. El inconveniente que se presenta

es que la señal de salida se verá reducida en su valor P.P. (pico a pico) en la misma magnitud que la caída en

los diodos, pero esto no afecta el funcionamiento de las distintas etapas

digitales ya que igualmente supera ampliamente el valor intermedio hacia el

nivel alto y el bajo, de modo que cualquier integrado CMOS interpretará un 1

y un 0 sin dificultad. Tampoco habrá problemas si la

carga del transistor fuera un relé a pesar que en

lugar de recibir 12 V se alimentará con alrededor de 10 V ya que éstos

componentes funcionan perfectamente bien a partir de 9 V. Hay que tomar en cuenta que los

diodos también deben soportar la corriente de la carga de colector y conectar

los adecuados. CONMUTACIÓN CON OTRAS TENSIONES Veamos ahora como conmutar un relé mediante transistores, con diferentes tensiones en

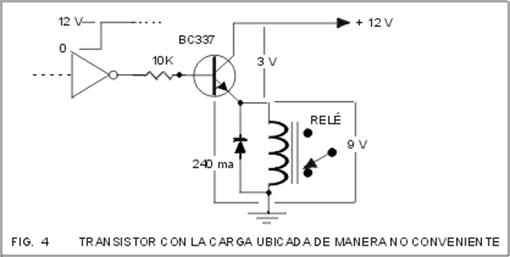

el circuito. Comenzamos por el caso que presentamos en la Fig. 4

Este es un caso que se observa con

cierta frecuencia en algunos equipos, y nos pareció importante citarlo. Nos

referimos a la ubicación de la carga, en éste caso el relé,

en el emisor de un transistor NPN. Sucede que de éste modo estamos

sumando la resistencia propia de la bobina del relé

a la que ofrece la juntura base-emisor, y en ésta condición la relación de

corriente de base y corriente de colector se ven alteradas, por ese motivo el

transistor no se satura a pleno y se produce una caída de potencial entre

colector y emisor; a modo de ejemplo la hemos establecido en 3 V, ya que

varía según la resistencia de base, por lo tanto al relé

llegan solo 9 V. Además sucede un hecho curioso que

puede llegar a desorientar al técnico, y es que el transistor no abastece

bien y sin embargo se calienta, lo que induce a pensar en reemplazarlo por

otro de mayor potencia. En realidad lo que pasa es que la

disipación de potencia que se produce en el transistor a raíz de la caída de

3 V es la causante de la temperatura del mismo. Aplicando la ley de Ohm vemos que: W = E

. I = 3 X 0,240 = 0,72 Watt Lo que es igual a 720 miliwatts,

y con ésta disipación el transistor se calienta. Si por alguna razón debemos mantener ésta disposición, hay

una solución que acomoda bastante bien las cosas. Se trata de aumentar la corriente de base a un valor mas

elevado pero que el transistor tolera perfectamente; hay que reducir la

resistencia de base a 1000 ohm ó un poco menos.

Ahora sí el transistor conducirá bien y la caída probablemente se reducirá a

1 V, con lo que la potencia disipada baja a 240 mW. De todos modos el transistor quedará ciertamente exigido

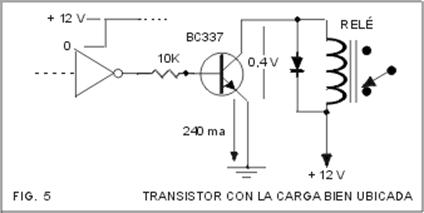

en su función. Ahora veamos que potencia disipa el transistor de éste mismo

circuito con la carga conectada como corresponde, de colector hacia +B.

Figura 5.

Ahora la situación cambia

notablemente, el transistor está saturado a pleno, la corriente de base es

mucho menor, la resistencia de polarización vuelve a ser de 10 K y la caída

que se mide en colector-emisor es como máximo de 0,4 V por lo tanto la

potencia disipada es: 0,4 X 0,240 = 0,096 W o sea 96 mW,

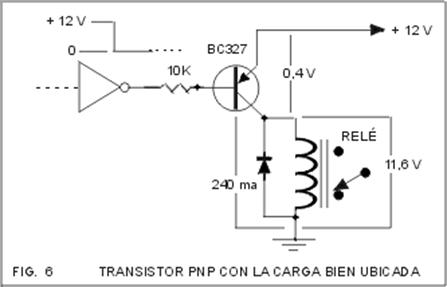

y con esta potencia el transistor trabaja frío. Lo expuesto es válido también para

los transistores PNP, pues sucede lo mismo que lo visto en la figura 4, en el

caso de conectar la carga de emisor a +B, ya que lo correcto es conectarla de

colector a masa. Figura 6. De acuerdo a lo expuesto se desprende

que siempre que sea posible LA CARGA SE APLICARA EN COLECTOR; EN

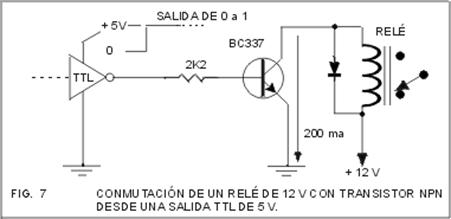

LOS NPN HACIA +B, Y EN LOS PNP HACIA MASA. Fig. 5 y 6 En los ejemplos siguientes se

observan otras formas de alimentar un relé cuya

bobina es para 12 V, partiendo de un circuito que posee integrados de la

familia TTL que están alimentados con una fuente de 5 V. Repetimos que a modo de ejemplo

utilizamos relés como carga y transistores

conocidos de uso corriente, pero pueden ser otras cargas y otros transistores

los que se usen para lograr los fines buscados.

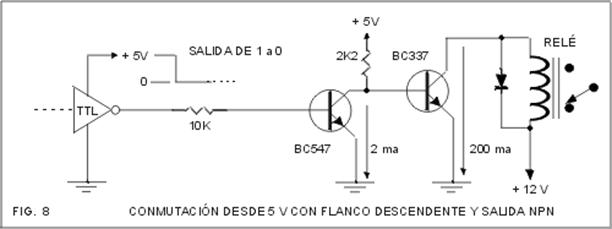

En la figura 7 observamos que el

separador cambia de estado con flanco ascendente, (de 0 a 1), con un

potencial de 5 V. Tratándose de un transistor NPN, no existe dificultad en su

conmutación porque como ya hemos visto, la base en situación de corte, está

efectivamente a potencial de masa (0) y para lograr su saturación solo es

necesario superar 0,7 V positivos, la salida del integrado es superior.

Supongamos un consumo en el relé de 200 ma. Para los cálculos

de polarización siempre se debe tomar el menor Beta (Hfe)

que indiquen los manuales, o sea que si dice 100 a 300, tomaremos

100. Veamos que corriente de base necesitamos de acuerdo a éstos datos.

Ib = Intensidad de base (en ma) - Ic = Intensidad

de colector - Hfe = Ganancia Ahora veamos que valor de

resistencia de base es necesario para lograr 2 ma con

una fuente de 5 V que es la salida que entrega el separador del ejemplo.

Se instalará el valor normalizado de 2,2 K

En la figura 8 vemos como lograr

la conmutación del relé con transistor de salida

NPN en los casos que el integrado entrega salida 0, o flanco descendente. Como vemos es necesario agregar un

transistor de baja potencia, ya que la corriente que debe manejar es la de

base del de salida, que ya vimos es de 2 ma. Mientras el integrado se encuentra

en 1 el BC547 conduce y envía a masa la base del BC337, de éste modo, se

mantiene al corte. Cuando el integrado cambia de

estado y pasa a 0, el 547 pasa al corte y su colector queda

"abierto", ahora si se polariza la base del 337 y se satura

conmutando el relé.

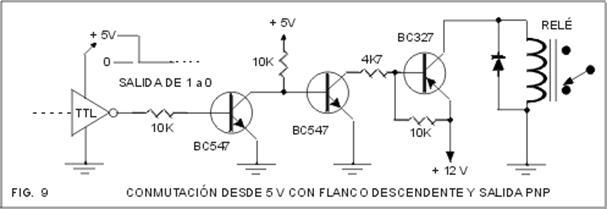

En la figura 9 vemos una situación

un tanto mas compleja que las anteriores, ya que, como hemos dicho, no se

puede mantener al corte con 5 V un transistor PNP que está alimentado con 12

V en el emisor. En éste caso no queda otro recurso que emplear 2 transistores

adicionales del tipo BC547, o sea de baja potencia. El funcionamiento es el siguiente:

Mientras el integrado está en reposo, la salida del mismo se corresponde con

la alimentación o sea de 5 V, y alimenta la base del primer transistor 547

con lo cual éste está saturado, por lo tanto su colector está en cero; el

segundo 547 se encuentra al corte por tener su base unida con el colector del

primero. Al estar al corte, el colector se encuentra en estado de alta

impedancia ó "colector abierto". En ésta situación la base del

BC327 está polarizada con tensión de 12 volt a

través de la resistencia de 10 K, por lo tanto también está al corte. Cuando el separador cambia de estado,

su salida pasa a 0, y se produce todo lo contrario a lo explicado. El primer

transistor 547 se corta, la base del segundo se torna positiva y se satura,

con lo cual envía a masa la base del 327 a través de la resistencia

de 4,7 K y se satura también, por lo tanto se conmuta el relé. ACOPLAMIENTO DE INTEGRADOS CMOS A

TTL CON TRANSISTORES Previamente haremos un repaso del

funcionamiento de los integrados CMOS y TTL para comprender a que se debe la

incompatibilidad de los mismos y porque es necesario acoplarlos entre si por

medio de transistores. Las características de la familia

de integrados CMOS difieren notablemente de los TTL en cuanto a alimentación,

lo que trae aparejado que salvo algunas excepciones no sean compatibles entre

si en forma directa. Los integrados CMOS pueden ser

alimentados con tensiones desde 3 V a 18 V, como límite, siendo lo

recomendado de 3 a 15 V. El drenaje de corriente que posibilitan

varía notablemente con éstas tensiones, por regla general se obtienen los

siguientes valores típicos, considerando la temperatura de trabajo en 25º C. Alimentados con fuente de 5 V,

drenan en su salida alrededor de 0,8 ma en

su nivel alto o bajo, es decir que "entregan o absorben" ésta

corriente. Si la alimentación fuese de 10 V,

la salida será de 2,2 ma, y si los alimentamos

con 15 V aumentará hasta 8 ma. La impedancia de entrada es muy

elevada, esto hace que prácticamente no exista consumo en la misma, por

consiguiente las etapas que los alimentan no se ven sometidas a carga alguna. El consumo propio en estado de

reposo, sin carga aplicada, es muy reducido y si bien varía según la

alimentación, podemos decir que está alrededor de 5 ua (microamper). Los tiempos de propagación y

transición en los cambios de estado, también varían notablemente con la

alimentación, a título informativo podemos estimar entre 30 y 100 ns (nanosegundos). Con la frecuencia de operación de

reloj también sucede lo mismo entre los distintos integrados, como referencia

diremos que está entre 3 y 12 Mhz (Megahertz). En cuanto a la familia

TTL las cosas son bien distintas como podemos apreciar. En éstos, el voltaje de

alimentación es de 5 V y su diseño es tal que ésta tensión no debe

sobrepasarse ya que se destruirán. En la práctica podemos tomar como valores

límite, una variación de + - 10% de ésta tensión. La corriente de salida está

en el orden de 16 ma en su estado alto ó

bajo, o sea la corriente que entregan o absorben. La importancia de éste hecho es

que la baja impedancia y capacidad de manejar intensidades de la etapa de salida

permite excitar otras etapas de manera directa, como por ejemplo, relés de baja corriente, diodos led con

su correspondiente resistencia de limitación etc,

siempre considerando el máximo de 16 ma antedicho. La entrada de éstos integrados, al

contrario de los CMOS, es de baja impedancia, y además consumen 1,6 ma para mantenerse en estado bajo (0). De lo expuesto se deduce que un

integrado TTL en su etapa de salida puede ser cargado por 10 entradas, o lo

que es lo mismo, abastece a 10 integrados. Los circuitos TTL se emplean en

ordenadores dada su gran rapidez de respuesta; el tiempo de transición y

propagación, es decir lo que tarda en pasar de 0 a 1 o viceversa,

es de aproximadamente 10 ns (nanosegundos), dependiendo del tipo de circuito. Se pueden obtener velocidades aun

mayores empleando la serie 74H, pero en éste caso también aumenta el consumo

propio, que ya de por si es elevado. La frecuencia de reloj que se

puede lograr en integrados TTL es sustancialmente mayor que en los CMOS, en

algunos de ellos se puede superar los 50 Mhz. Resumiendo, podemos decir que los

integrados CMOS tienen ciertas ventajas con respecto a los TTL, como ser,

mucho menor disipación de corriente (bajo consumo), alta impedancia de

entrada, lo que permite alimentar muchos otros desde una salida (mas de 50),

amplia gama de tensiones de alimentación. Pero se encuentran en inferioridad

en: menor corriente de salida, menor velocidad de conmutación o

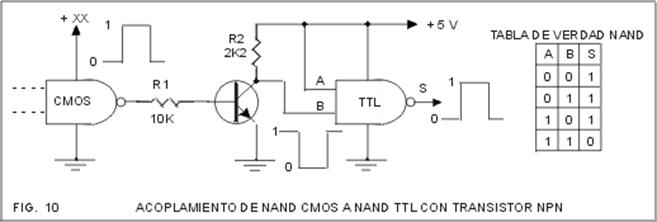

transición, y menor frecuencia de reloj. Veamos a continuación en la figura

10 un acoplamiento de un integrado CMOS a otro TTL por medio de un

transistor.

El ejemplo está representado por dos

compuertas NAND y la transferencia de una a otra se efectúa mediante un

transistor NPN. En estado de reposo la

compuerta NAND TTL tiene sus dos entradas a nivel lógico 1, una de ellas

a través de la resistencia de 2,2 K, por consiguiente según su tabla de

verdad la salida está en nivel 0. Cuando la compuerta NAND

CMOS cambia de estado y pasa a nivel 1, el transistor se satura

llevando la entrada B a nivel 0, por lo tanto la salida

TTL cambia a 1; según la tabla, A1 y B0 = S1. La alimentación del integrado CMOS

(+XX) carece de importancia en éste caso (puede estar entre 3 y 15 V)

pues la entrada B del TTL depende solo del + 5 V y la conmutación

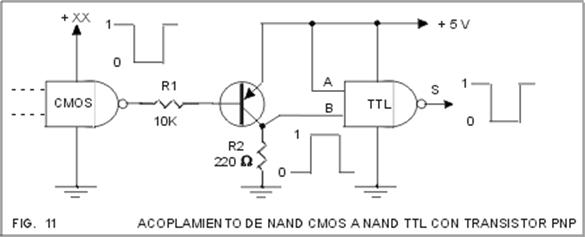

del transistor. En la figura 11 vemos un caso

similar pero con los pulsos de salida de nivel contrario al anterior y con un

transistor PNP como acoplamiento.

Ahora tenemos las entradas A y B

TTL con niveles 1 y 0 respectivamente por lo tanto la salida está en 1;

cuando el CMOS cambia a 0, el transistor conduce y envía un 1 a la

entrada B, y según la tabla de verdad, A1 y B1 = S0. Vamos a hacer una

aclaración que es muy importante. Se habrá observado que en la

figura 10, R2 tiene un valor de 2,2 K y en la figura 11 de 220 Ohm, esto se debe a lo siguiente : Las entradas de los

integrados TTL consumen 1,6 ma como ya se

ha dicho, PARA MANTENER EL ESTADO 0 (cero); si necesitáramos un estado lógico

1, no hay inconvenientes en darlo a través de una resistencia de valor relativamente

elevado ya que con 1 no hay consumo, tal es así que si dicha entrada quedara

"al aire" sin conexión, el integrado interpretará un 1. De manera que el 1 que

recibe la entrada B a través de R2 de 2,2 K en la fig. 15, es

correcto y podría ser mayor aún éste valor que nada sucedería. Cuando el transistor cierra a

masa, la entrada B drena el 1,6 ma a

través de el y queda en 0V. Pero en la figura 11 la

entrada B tiene que estar a nivel 0 a través de una

resistencia, y como por ésta ha de circular 1,6 ma,

se establecerá una caída de potencial cuya magnitud depende del valor óhmico

de ella, de manera que tiene que ser un valor suficientemente bajo para que

la caída sea pequeña y el integrado interprete un 0, y al mismo tiempo no

sobrecargar al transistor en el instante que conduce. Haciendo uso de la ley de Ohm veamos que potenciales tenemos con una y otra

resistencia. Necesitamos saber que caída de

tensión tenemos en la resistencia sabiendo que por ella circularán 1,6 ma, por lo tanto: E = I

. R = 0,0016 X 2.200 = 3,52 Volt Quiere decir que con una

resistencia de 2,2 K el integrado no interpretará el 0 sino un 1, por lo

tanto no funcionará éste circuito. Ahora veamos cambiando éste valor

por 220 Ohm. E = I

. R = 0,0016 X 220 = 0,35 Volt Con éste valor la entrada

B está a 0 sin ninguna duda y el circuito funcionará normalmente. Veamos ahora que carga soporta el

transistor con ésta resistencia.

Como vemos la carga para el

transistor es de 22,7 ma y ésta cifra la

soporta cualquier transistor sin dificultad. El ejemplo expuesto bien podría

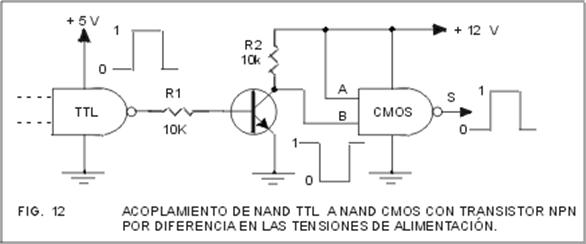

darse a la inversa, es decir tener la necesidad de acoplar la salida de un

TTL a la entrada de un CMOS, en la figura 12 se observa como hacerlo.

Como vemos en la fig. 12, el circuito de acoplamiento es

igual, ya que la tensión de alimentación de la entrada B CMOS, depende

de la fuente de 12 V para lograr el estado alto, y de la conmutación del

transistor para el estado bajo. La salida TTL, de 5 V, solo se

utiliza para polarizar la base del transistor y lograr de éste modo la

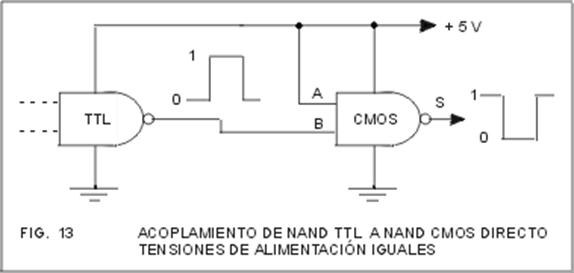

saturación y el corte del mismo. Si las tensiones de alimentación

de los dos integrados fueran las mismas; en éste caso de 5 V ambos, ya que el

TTL no permite otra, el acoplamiento puede realizarse en forma directa.

Recuerde que los CMOS no consumen corriente en sus entradas, por lo tanto un

TTL podría abastecer gran cantidad de integrados CMOS. Figura 13.

Hemos visto una cantidad de

circuitos de aplicación de transistores y la forma de polarizarlos

correctamente para su uso en conmutación, el tema es mas amplio

aún, pero con lo visto en la presente lección, el alumno no tendrá

dificultades para emplearlos en cualquier circuito digital que se le

presente. A partir de la presente lección

vamos a realizar varios trabajos prácticos en la plaqueta de ensayos (Protoboard), además de los que se arman en plaquetas de

circuito impreso, a fin de llevar a la práctica los conocimientos que va

adquiriendo. Es muy importante que el alumno

efectúe los trabajos expuestos, pues la experiencia que irá adquiriendo al

poder comprobar el funcionamiento de los elementos usados incide notablemente

en la formación técnica que todos deseamos sea de la mejor calidad. RADIO INSTITUTO |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

E-mail: radioinstituto@gmail.com - Sitio web: www.radioinstituto.com.ar |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||